- 全部

- 默认排序

随着芯片制造工艺的不断进步,单个芯片的晶体管数量持续增长,从数万级别到今天的数百亿级别,虽然后面会迎来万亿级芯片时代。长期以来,提高晶体管密度抑制是实现大规模集成电路的主要途径,厂商及工程师的关注点也是以芯片制程的升级为主。但随着工艺邻近物

这里差分可以这样走这里铜皮要把焊盘和过孔包住bga后面的电容没有连接以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://item.taobao.com/item.htm

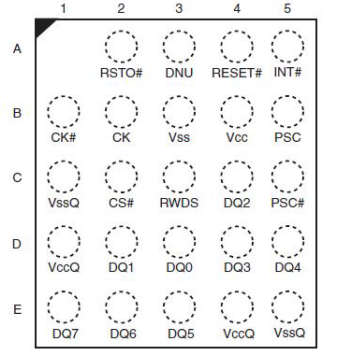

一、HyperFlash NOR 闪存概述S26KS128S(128Mb)HyperFlash™ NOR闪存采用小型 8x6mm 球栅阵列 (BGA) 封装,与 Quad SPI 和双 Quad SPI 部件共享一个共同占位面积,以简化电路

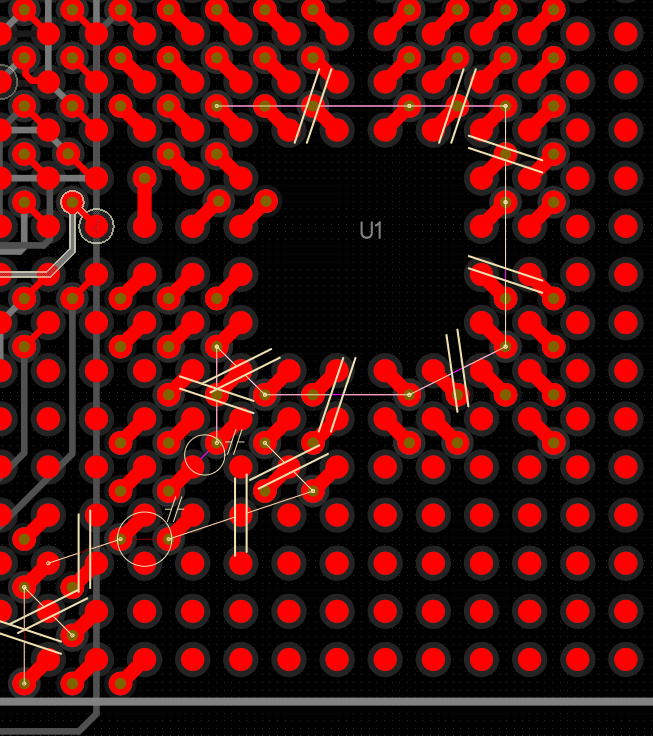

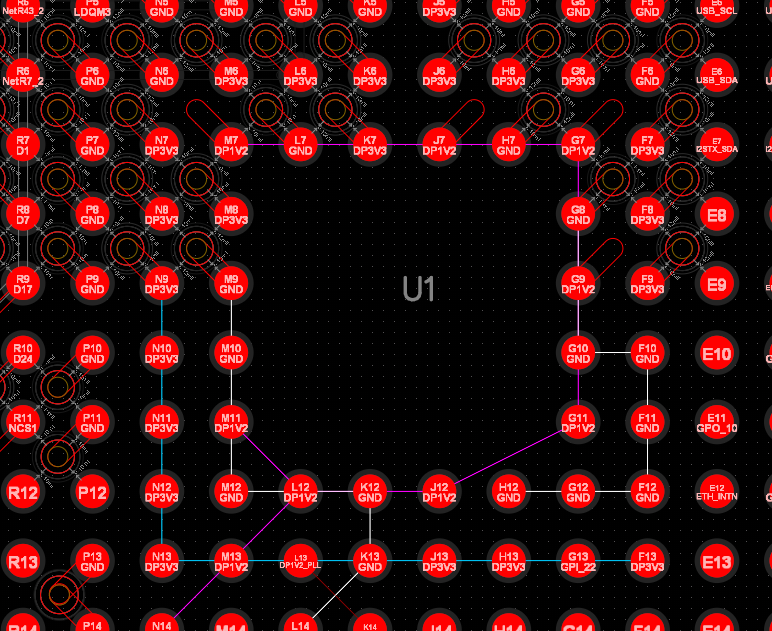

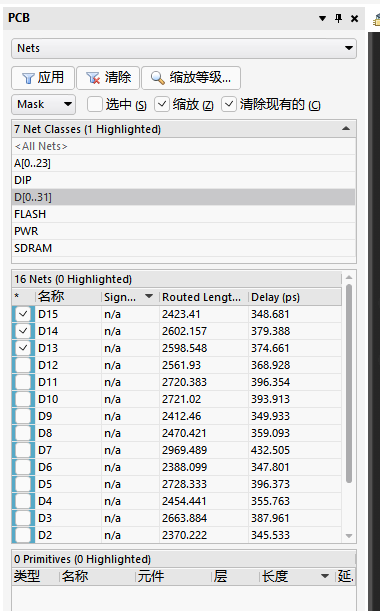

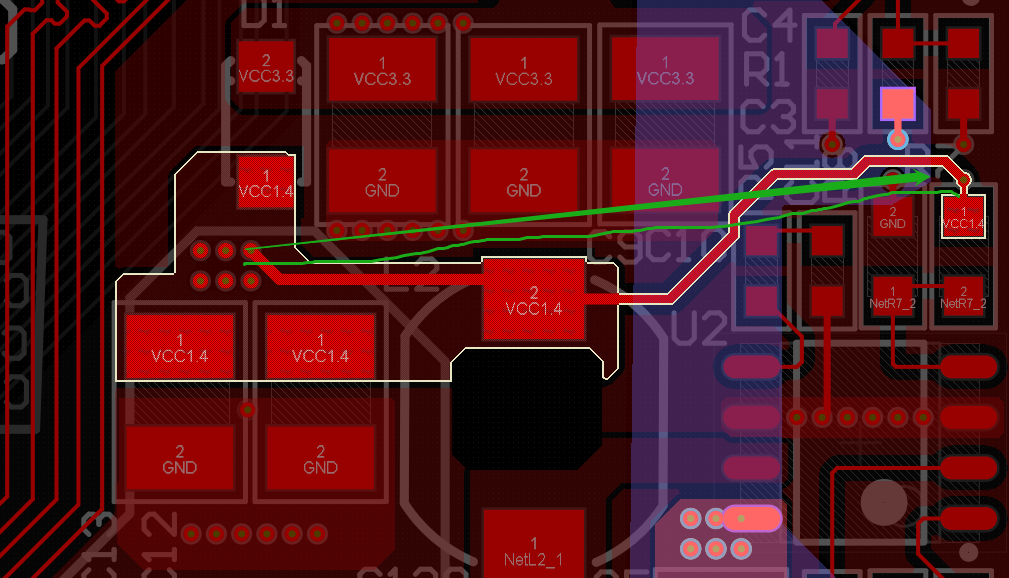

BGA内的电源并未处理,注意要么铺铜要么在电源层进行分割:注意看下U1-U16的地址控制时钟需要组内满足误差 ,还存在报错 ,重新组内等长:U16-U17的地址控制时钟注意对内的等长误差,还存在报错:数据线内也存在等长误差报错:数据线之间满

GND跟电源网路都没有处理:地址线都有及个别的没有跟BGA内的扇孔连接:等长线的GAP尽量大于等于3W,不要太短了:数据线一组走线尽量紧凑点:看下是否存在间距报错:等长线之间要满足3W间距原则:上述一致问题,等长线GAP满足下3W长度:间距

作为电子工程师,在工作过程中总会遇见各种各样的问题,部分让人头痛,也会让人绝望崩溃,下面来看看有哪些最痛苦绝望的问题,是电子工程师不想再遇见。1、永远无法解决的电磁噪声2、芯片不受控制,甚至重启也没用3、某宝劣质焊锡、烙铁头4、电源环路不稳

注意地址线之间等长需要满足3W2.电感中间挖空,中间就尽量不要铺铜,后期自己调整一下3.模拟信号走线需要加粗反馈线需要加粗到10mil.丝印,过孔尽量不要上焊盘5.过孔需要盖油处理6.顶层BGA里面额铜可以挖掉以上评审报告来源于凡亿教育90

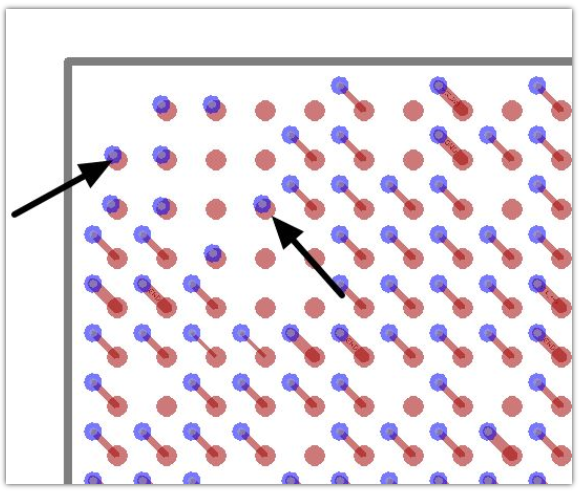

对于BGA扇孔,同样过孔不宜打孔在焊盘上,推荐打孔在两个焊盘的中间位置。很多工程师为了出线方便,随意挪动BGA里面过孔的位置,甚至打在焊盘上面,如图1所示,从而造成BGA区域过孔不规则,易造成后期焊接虚焊的问题,同时可能破坏平面完整性。图1

数据线分组错误2.地址线分组错误3.焊盘出线不规范,焊盘中心出线至外部才能拐线处理,避免生产出现虚焊4.走菊花链的结构,等长应该是BGA到SDRAM,然后再从SDRAM到FLASH5.相邻焊盘是同网络的,不能直接相连,需要先连接焊盘之后在进

反馈要从电容后面取样2.注意过孔不要上焊盘3.走线尽量不要从电阻电容中间穿4.丝印调整不到位,注意丝印不要上焊盘5.顶层BGA里面的铜尽量挖掉6.此处走5mil地线太细,建议最少12mil以上以上评审报告来源于凡亿教育90天高速PCB特训班

扫码关注

扫码关注